# Volume Mount Devices

$\mathbf{b}\mathbf{y}$

#### Alan Han

#### B.S. Electrical Engineering, Purdue University (2018)

#### Submitted to the Program in Media Arts and Sciences, School of Architecture and Planning, in partial fulfillment of the requirements for the degree of

#### Master of Science

# at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY May 2025

#### © 2025 Alan Han. All rights reserved.

The author hereby grants to MIT a nonexclusive, worldwide, irrevocable, royalty-free license to exercise any and all rights under copyright, including to reproduce, preserve, distribute and publicly display copies of the thesis, or release the thesis under an open-access license.

| Authored by:  | Alan Han<br>Program in Media Arts and Sciences<br>May 16, 2025                         |

|---------------|----------------------------------------------------------------------------------------|

| Certified by: | Prof. Neil Gershenfeld<br>Director, MIT Center for Bits and Atoms<br>Thesis Supervisor |

| Accepted by:  | Tod Machover<br>Academic Head, Program in Media Arts and Sciences                      |

# Volume Mount Devices

by

#### Alan Han

Submitted to the Program in Media Arts and Sciences, School of Architecture and Planning, on May 16th, 2025 in partial fulfillment of the requirements for the degree of

#### Master of Science

#### Abstract

As Moore's Law ends and AI demands increasingly tax our climate and resources, the limitations of two-dimensional electronics integration have become critical bottlenecks. Surface-mount devices (SMDs) remain entrenched in industry practice despite being insufficient for today's computing challenges and sustainability needs. This thesis introduces the volume mount device (VMD), a three-dimensional electronics packaging standard that bypasses the traditional dieto-server stack while offering a scalable, reversible framework inspired by natural ecosystems' circularity.

The VMD approach embeds both electrical function and mechanical structure into modular elements that assemble freely in 3D space. Rather than building circuits on planar PCBs, this system constructs functional circuits by linking components into a self-constraining lattice architecture. My current implementation leverages existing supply chains by incorporating SMD components on small tile PCBs, while establishing a pathway toward eventually replacing SMDs at the IC packaging level.

I developed a hybrid assembly system combining 3D printing and pick-and-place automation to build multi-layered electronic assemblies efficiently. Where prior work achieved only tens of parts at hundreds of components per hour (CPH), my system demonstrates automated assembly of hundreds of integrated elements at approximately 1000 CPH. I evaluate various geometric configurations, assess performance overhead compared to conventional approaches, and develop cost-effective, self-aligning connector interfaces for reliable joints—creating a foundation for electronics systems that can be assembled, disassembled, and reassembled as needed while improving resilience against supply chain disruptions.

Thesis supervisor: Prof. Neil Gershenfeld Title: Director, MIT Center for Bits and Atoms

# Volume Mount Devices

$\mathbf{b}\mathbf{y}$

Alan Han

This thesis has been reviewed and approved by the following committee members:

Prof. Neil Gershenfeld

Director, Center for Bits and Atoms Professor, Media Arts and Sciences Massachusetts Institute of Technology

Prof. Ahmad Bahai

Senior Vice President and Chief Technology Officer, Texas Instruments Professor of the Practice, EE Massachusetts Institute of Technology

Prof. Joseph Jacobson

Associate Professor of Media Arts and Sciences Massachusetts Institute of Technology

### Acknowledgements

Thank you to everyone who has supported me along the way, I am beyond grateful and could not have made this journey without you.

I'd like to start by thanking Neil, for creating this amazing space with amazing people and tools, and challenging me to rethink what I'm capable of. Thank you to my readers Joe and Ahmad, for your support and insight as I developed this thesis.

Thank you to the CBA of past, present, and future, as well as visitors, UROPs, and friends of the lab, for making the basement a lively community: Quentin, Nik, Jake, Alfonso, Miana, Kat, Jiaming, Marcello, Shravika, Kerdeem, Yohan, Ric, Leo, Cedric, Dave, Zach, Will, Amira, Camron, Alex, Erik, Sara, Paul, Scott, Nicole, Eyal, Jack, Francisco, and Vlasta.

Thank you Miana, for convincing me to apply, for which I'm glad I did. Thank you to the usual suspects, Quentin and Nik, and Jake, and Alfonso, who always seem to look out for me. Thank you Erik, for providing the architectural foundation for this project and giving me an excuse to decorate my keyboard with new symbols, and for being patient with my many questions. Thank you Zach, Will, and Jonathan, for pioneering discrete electronics in the CBA and for providing invaluable reference points. I stand on your shoulders.

To my Media Lab community: thank you Retroentomologists and Followers; especially Michael, Ana, Char, Nathan, Lucy, Eleanor, Sarah, Gauri, Isabella, Perry, and Lancelot. Our cohort kept me cohesive and you put the magic in the media lab for me. Sarah, Otto, and Dave, thank you for our game-of-thrones caliber commander games. Cedric, thank you for always being down to hack something and organizing the Shenzhen trip for which I am grateful for.

Thank you Foppers and Triangles back home, especially Amy, Cecilia, Emily, Satyo, and Ed, for keeping me sane, and keeping me grounded. Thank you James, for your lifelong friendship. To my fellow Boilermakers, thank you Ryan and Nathan for the diving and supreme commanding. Thank you Charles and David, for formally solving problems with me and blowing up my phone with 500 notifications about naval doctrine and kiminonawa.

Thank you to everyone at Molex, and especially Vic for getting me obsessed about finding new ways to package electronics in the first place.

Thank you CBA sponsors and grant providers, for supporting our work and sharing our excitement for where it goes. Thank you CBA staff for keeping things running, John, Joe, Hannah, Kara, Candace, Dan, Marissa, and Sherry.

And last but not least, thank you to my family, Mom, Dad, and Angel, for your unconditional love, support, and snacks.

# **Table of Contents**

| 1 Introduction                                       | .17  |

|------------------------------------------------------|------|

| 1.1 Motivation                                       | . 17 |

| 1.2 Electronics Packaging                            | .18  |

| 1.2.1 Printed Circuit Boards                         | . 19 |

| 1.2.2 Integrated Circuit Packaging                   |      |

| 1.2.3 Heterogeneous Integration                      |      |

| 1.3 Supply Chain Challenges and Climate Implications | . 20 |

| 1.4 Accessible Modularity                            | 20   |

| 1.5 Related Work                                     |      |

| 1.5.1 Project Tinkertoy                              | . 21 |

| 1.5.2 Electronic Digital Materials                   | .21  |

| 1.6 Thesis Contributions and Overview                | . 25 |

| 2 Volume Mount Devices (VMDs)                        | .28  |

| 2.1 Geometry Overview                                | .28  |

| 2.2 4Hx Family                                       | .31  |

| 2.2.1 4H                                             | .31  |

| 2.2.2 4Hp                                            | .31  |

| 2.3 4Bx Family                                       | .37  |

| 2.3.1 4B                                             | . 37 |

| 2.3.2 4BI                                            | . 39 |

| 3 Circuit Assembly System                            | .43  |

| 3.1 Assembly                                         | .43  |

| 3.1.1 Setup                                          | . 43 |

| 3.1.2 Operation                                      | . 45 |

| 3.2 Motion System                                    | . 45 |

| 3.3 Feeders                                          |      |

| 3.3.1 Passive Tray Feeders                           | . 45 |

| 3.3.2 Adding Depth                                   | . 46 |

| 3.3.3 Alternative Feeders                            | .48  |

| 3.3.4 Resetting Jobs                                 | . 48 |

| 3.4 Substrates                                       | .48  |

| 3.4.1 4Hp Macro-tile                                 |      |

| 3.4.2 4BI Template                                   |      |

| 3.4.3 Material Choice                                |      |

| 3.5 End Effector                                     | .51  |

| 3.5.1 Claw Gripper                                   |      |

| 3.5.2 Vacuum Nozzle                                  |      |

| 3.5.3 Sealing the Vaccuum                            |      |

| 3.5.4 Nozzle Geometry                                |      |

| 3.5.5 Tile Surface Planarity and Area                |      |

| 3.6 Error Correction                                 |      |

| 3.6.1 Overconstraint and Compliance                  |      |

| 3.7 Comparative Assembly Rates                       | . 57 |

| 3.7.1 Possible Parallelization Pathways              | 59  |

|------------------------------------------------------|-----|

| 4 Testing and Performance Overhead                   | 62  |

| 4.1 Joint Reliability                                | 62  |

| 4.1.1 4Hp H-eon Elements                             | 62  |

| 4.1.2 4BI Pad-to-Pad                                 | 62  |

| 4.1.3 4BI Pad Geometry                               | 62  |

| 4.2 Circuit Performance                              | 70  |

| 4.2.1 Ring Oscillators                               | 70  |

| 4.2.2 Logic Gates                                    | 70  |

| 4.2.3 Full Adders                                    | 70  |

| 4.3 Scaling Performance Projections                  | 73  |

| 4.3.1 Capacitance                                    | 73  |

| 4.3.2 Inductance                                     | 75  |

| 4.3.3 Resonance Frequency                            | 76  |

| 4.3.4 Capacitive Switching Energy                    | 76  |

| 4.3.5 Projections from 10mm down to 10nm             |     |

| 5 4BI Connector (4BIc)                               |     |

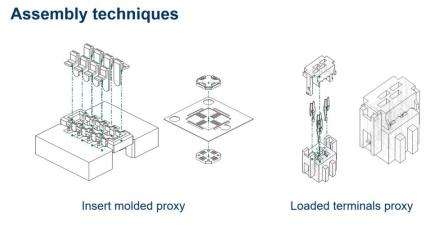

| 5.1 Electrical Connectors in a Day (eCiD)            |     |

| 5.1.1 Assembly Techniques                            |     |

| 5.1.2 Housings                                       |     |

| 5.1.3 Leadframes                                     |     |

| 5.1.4 Process Registration                           |     |

| 5.2 4BIc Geometry                                    |     |

| 5.2.1 4BIc Process Steps Overview                    |     |

| 5.2.2 Panelized PCBs                                 |     |

| 5.2.3 Leadframe Fabrication                          |     |

| 5.2.4 Ejecting Trash                                 |     |

| 5.2.5 Form 1 Tooling for Leadframe                   |     |

| 5.2.6 Formed Leadframe                               |     |

| 5.2.7 Form 2 Tooling for Leadframe and Pcb           |     |

| 5.2.8 Tool Singulation of Pcb Panel                  |     |

| 5.2.9 Advancing VMDs                                 |     |

| 6 Conclusion                                         |     |

| 6.1 Future Work                                      |     |

| 6.1.1 Finishing 4BIc                                 |     |

| 6.1.2 Assembly Improvements                          |     |

| 6.1.3 Geometric Exploration for Enhanced Reliability |     |

| $6.1.4 \text{ 4Cx Family} - 4C, 4Ci, 4Ce, 4Cs \dots$ |     |

| 6.1.5 uVMDs and nVMDs                                |     |

| 6.1.6 Mini-Assembly Farms for Smaller Elements       |     |

| 6.1.7 Super-DICE 2.0                                 |     |

| 6.2 Impact                                           |     |

| Bibliography                                         | 107 |

# List of Figures

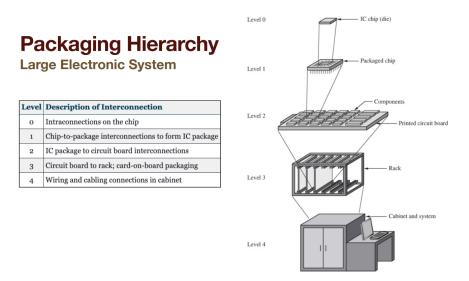

| 1.1 Hierarchy of electronics packaging levels. Level 0 represents the bare die               |

|----------------------------------------------------------------------------------------------|

| (transistors). Level 1 is the integrated circuit (IC) package. Level 2 consists of the       |

| substrate (e.g., PCB). Level 3 refers to the full system                                     |

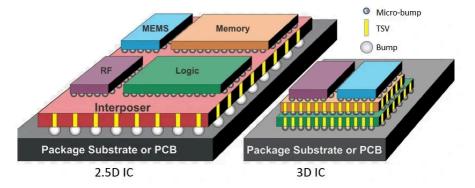

| 1.2 Different Heterogeneous Integration approaches                                           |

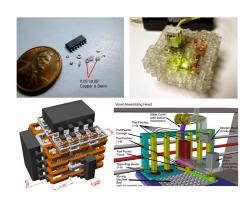

| 1.3 Digital electronic materials history, Neil Gershenfeld                                   |

| 1.4 Basic Bulk Materials                                                                     |

| 1.5 Component Materials                                                                      |

| 1.6 Integrated Materials                                                                     |

| 1.7 Component level, in-between basic and integrated                                         |

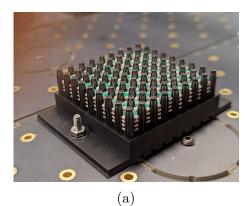

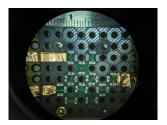

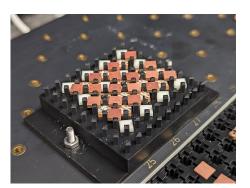

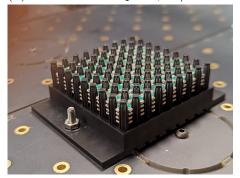

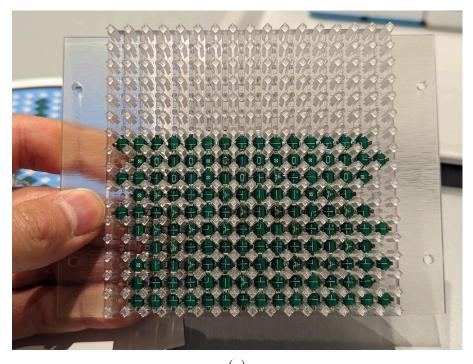

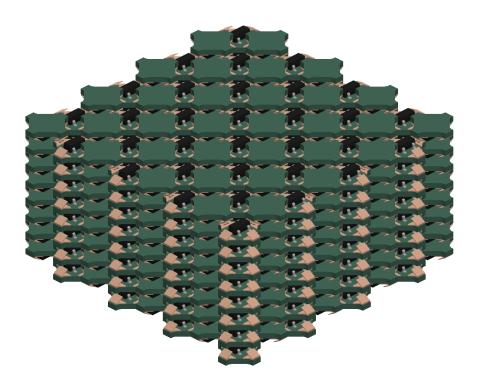

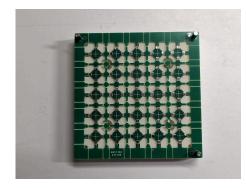

| 2.1 4BIc0 circuit assemblies: 4BIc0 8-layer mechanical benchmark (254/256 tiles)             |

| automatically assembled in ~14min (a); 4BIc0 2-layer stackable full-adder circuit (146       |

| tiles) manually assembled in ~55min (b)                                                      |

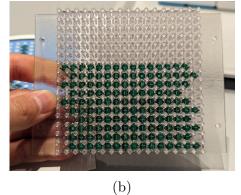

| 2.2 Å variety of geometry iterations                                                         |

| 2.3 Fabricated geometry families                                                             |

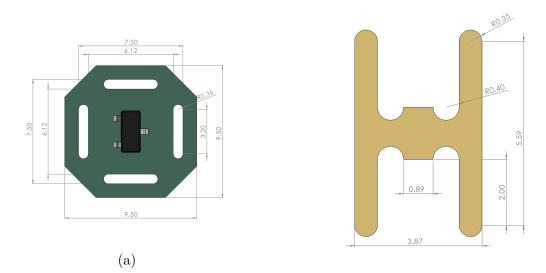

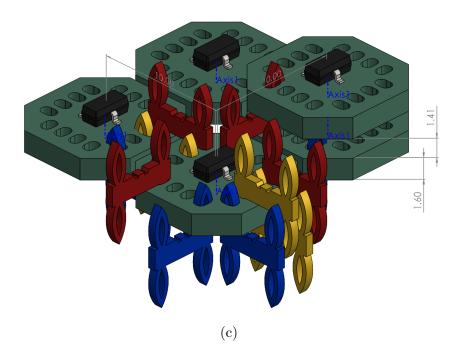

| 2.4 4H dimensions: the tile (a), the H connector (b), and the lattice (c)                    |

| 2.5 4H overview                                                                              |

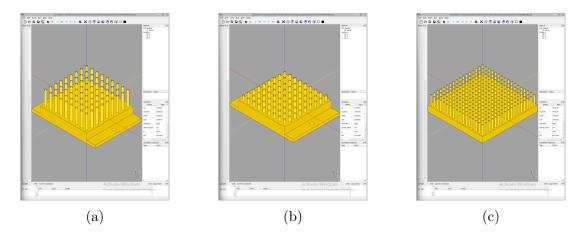

| 2.6 4Hp: the tile (a), the connector (b), and the lattice (c)                                |

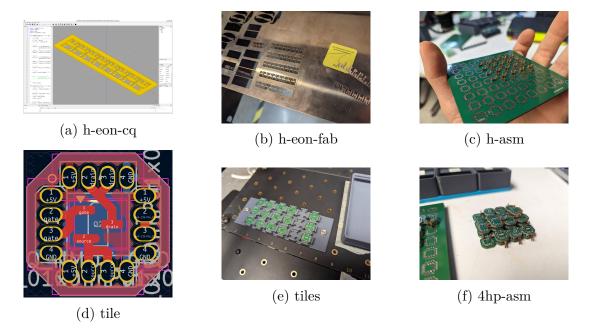

| 2.7 Top: H-eon, from cad to fab, Bottom: 4Hp tile, from cad to fab                           |

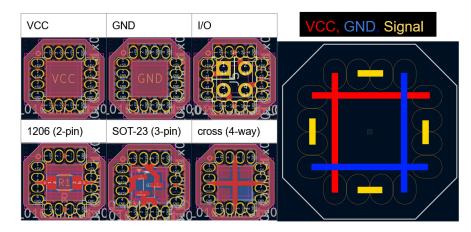

| 2.9 left, basic 6-tile library; right, implemented power, ground, and signal mapping for     |

| tiles                                                                                        |

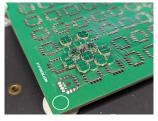

| 2.10 4Hp Batch 009 tiles                                                                     |

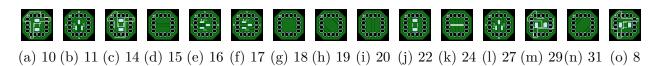

| 2.11 Hierarchical assembly of tiles and macro-tiles, which enable error-correction at        |

| larger, block-sized scales                                                                   |

| 2.12 4B design and assembly tests                                                            |

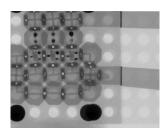

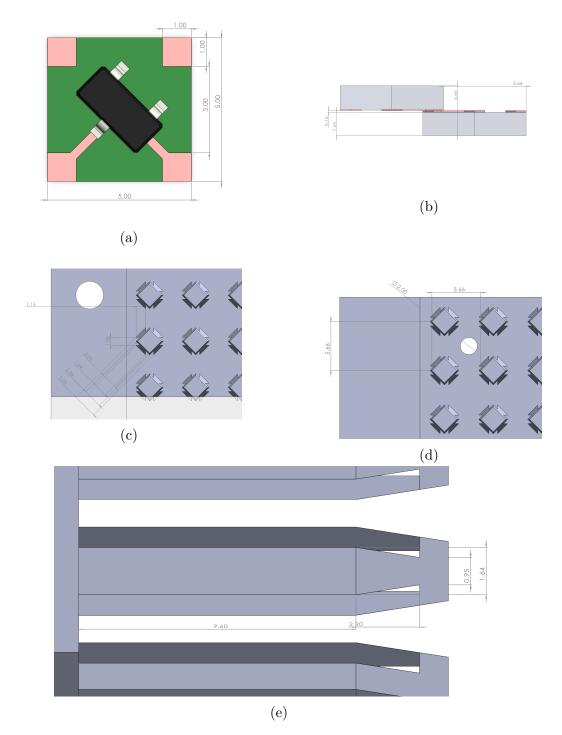

| 2.13 4BI dimensions: 4BI tile (a), 4BI lattice pitch (b), 4BI template top down (c),         |

| template corner features (d), and side profile of flexures (e)                               |

| 2.14 initial 4BI geometry concept and prototypes (Neil Gershenfeld)40                        |

| 2.15 4BI tiles                                                                               |

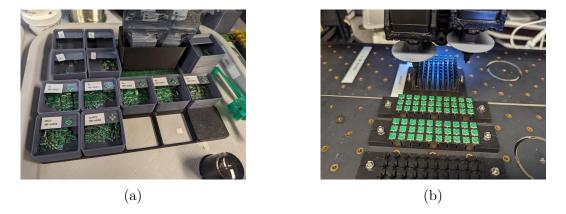

| 2.16 4BI tiles in gridfinity bins for storage (a), and tiles loaded in a feeder for assembly |

| (b)                                                                                          |

| 3.1 Benchmark tests                                                                          |

| 3.2 The assembler picking and placing from 4BIc0 feeders                                     |

| 3.3 Basic PnP operation (without computer vision): picking (a), moving (b), placing (c)      |

| 45                                                                                           |

| 3.4 LumenPnP                                                                                 |

| 3.5 Parametric feeder design in CadQuery: 30 element capacity 3x10_feeder (a), 60            |

| element capacity 3x20_feeder (b), 60 element capacity 6x10_feeder (c); evolution of          |

| feeder concepts for 4Hp, from trays to magazine dispensers (d)                               |

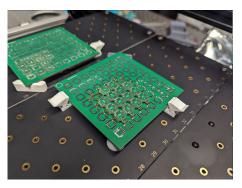

| 3.6 4Hp macro tiles as substrates                                                            |

| 3.7 Parametric template design in Cadquery: 9x9x10 template, 320 element capacity            |

| (a), 9x9x3 template, 96 element capacity (b), 17x17x10 template, 1280 element capacity       |

| (c)                                                                                          |

| 3.8 Templates in use for various tasks: early rigid template with poor tolerance (a),        |

| high-temp reflow variation from soldering tests (b), matured design using Form 4 Black V5 (c)                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

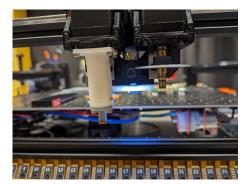

| 3.9 Evolution of tile gripper designs for 4Hp523.10 Passive gripper end effector for 4Hp H-eon connector533.11 4BI error states: failure to rotate, tile never enters template (a), tile not                                                                                  |

| completely flush; opportunity to correct but may interfere with adjacent placements (b), tile placed on its side; tile enters template but is invalid and affects adjacent tiles (c) 55 3.12 Vaccuum end effector: Tile tilting due to uneven solder, center support (a), CAD |

| of end effector supporting tile on edges, even force distribution (b)                                                                                                                                                                                                         |

| 4.1 4BI experiments to try and solve intermittency: Spring-loaded compression cap (a), solder and reflow (b,c), experimenting with plating finishes (d), introducing contact                                                                                                  |

| geometry via leadframes (e), mechanical decoupling of cable strain                                                                                                                                                                                                            |

| 4.3 At 5.655mm pitch, 1mm x 1mm pads (4BI-b001, b002) could easily result in only $\sim$ 25% pad overlap with underconstrained rotational error. 1.5mm x 1.5mm pads (4BI-b003+) increases this to $\sim$ 50%, with little downside. Reducing the pitch would                  |

| improve this even more                                                                                                                                                                                                                                                        |

| 4.4 4BIc contact improvements                                                                                                                                                                                                                                                 |

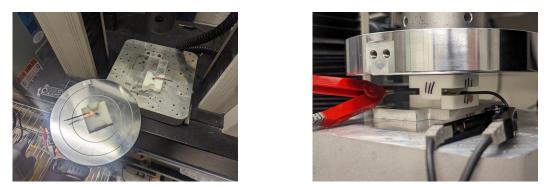

| soldering stranded wire to pyralux, solder joint to tile (b), test jigs fabricated for each of the 4 test finishes (c), test jigs in their closed state, ready for testing (d)                                                                                                |

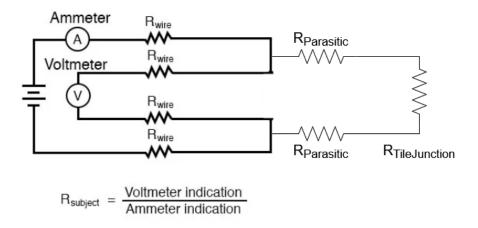

| 4.6 pad-to-pad resistance vs compression force test setup                                                                                                                                                                                                                     |

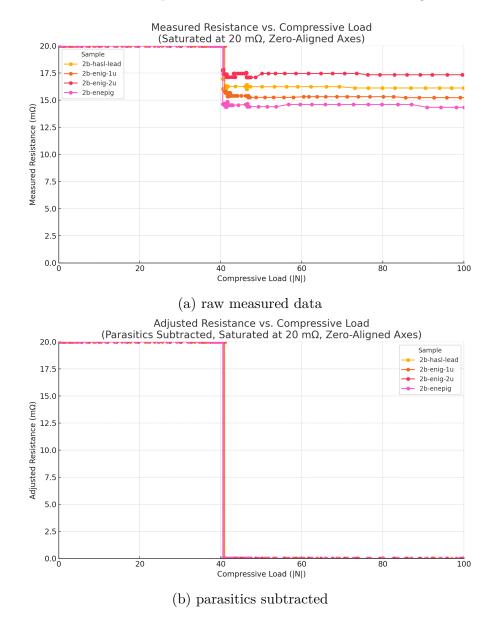

| 4.8 Plating finish test results, resistance vs compression load                                                                                                                                                                                                               |

| 4.10 2MHz resonant frequency 4Hp ring oscillator circuit: ring oscillator schematic (a),                                                                                                                                                                                      |

| 4Hp ring oscillator circuit (b), oscilloscope shot of circuit ringing (c), 4BIc0 ring<br>oscillator design in dice-cad (d)                                                                                                                                                    |

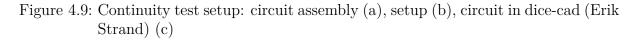

| 4.11 4Hp logic implementations: 4Hp diode AND gate (a), diode AND gate schematic (b), 4Hp nmos NAND gate (c), nmos NAND gate schematic (d)                                                                                                                                    |

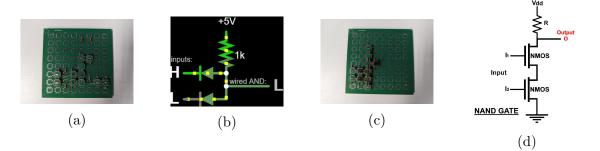

| 4.12 Adder circuits: Full-adder schematic (a), 4Hp Full-adder implementation (Shravika Pendyala) (b), 4BIc0 half-adder (c), 4BIc0 full-adder (d)                                                                                                                              |

| 4.13 ~146 tile 4BIc0 full-adder circuit assembled (a), and in test-setup (b)72                                                                                                                                                                                                |

| 4.14 modeling parasitic capacitance between two vertically neighboring tiles (in green), which may have different, partially overlapping routing patterns                                                                                                                     |

| 4.15 modeling parasitic inductance loop through the smallest possible routing loop<br>between 2x2 tiles                                                                                                                                                                       |

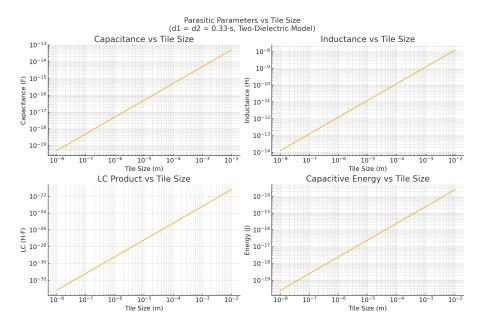

| 4.16 Parasitic Parameters vs Tile Size $(d1 = d2 = 0.33 * s, Two-Dielectric Model)$ :<br>Capacitance vs Tile Size (a), Inductance vs Tile Size (b), LC Product vs Tile Size (c),                                                                                              |

| Capactive Energy vs Tile Size (d)                                                                                                                                                                                                                                             |

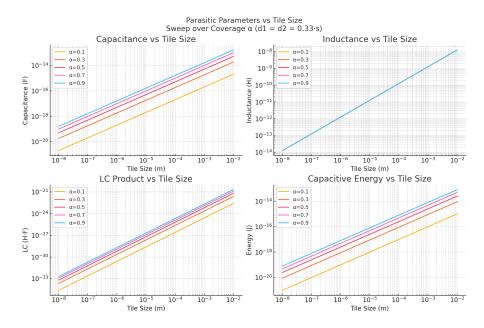

| Two-Dielectric Model): Capacitance vs Tile Size (a), Inductance vs Tile Size (b), LC                                                                                                                                                                                          |

| Product vs Tile Size (c), Capactive Energy vs Tile Size (d)                                                   |

|---------------------------------------------------------------------------------------------------------------|

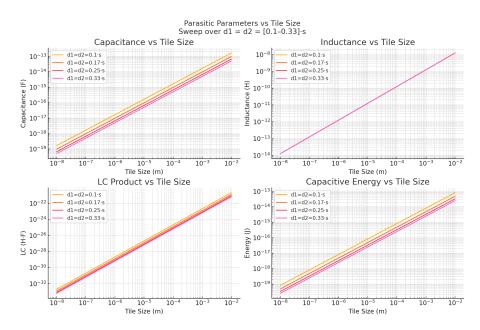

| 4.18 Parasitic Parameters vs Tile Size, Sweep over $d1 = d2 = [0.1-0.33] * s$ ,                               |

| (Two-Dielectric Model): Capacitance vs Tile Size (a), Inductance vs Tile Size (b), LC                         |

| Product vs Tile Size (c), Capactive Energy vs Tile Size (d)                                                   |

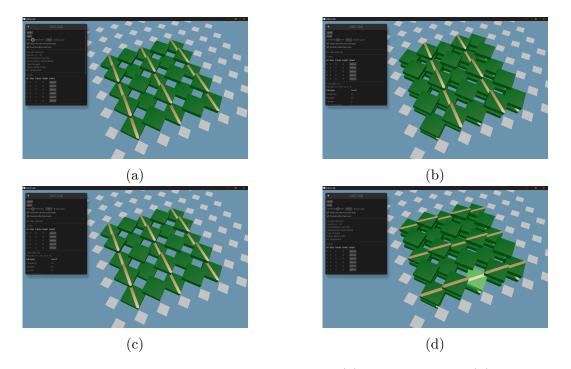

| 4.19 Routing considerations: parallel layer 1 (a), parallel layer 2 (b), crossed layer 1 (c),                 |

| crossed layer 2 (d)                                                                                           |

| 5.1 Connectors fabricated using a combination of desktop fabrication tools                                    |

| 5.2 Assembly techniques                                                                                       |

| 5.3 Printing supports for small connector housings                                                            |

| 5.4 Backside channels to alleviate cupping                                                                    |

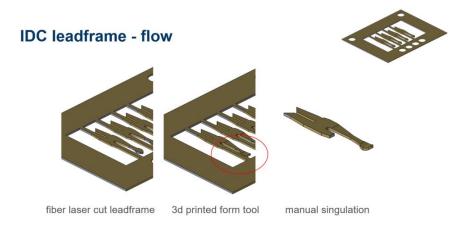

| 5.5 Leadframe flow for the IDC                                                                                |

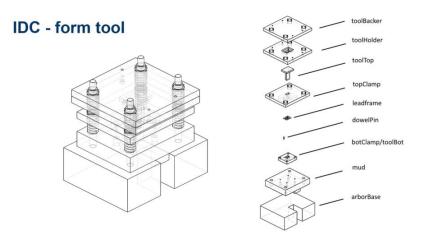

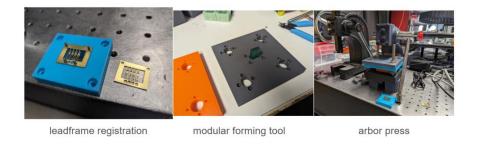

| 5.6 Form tool for the IDC                                                                                     |

| 5.7 Fabricated tools for the IDC                                                                              |

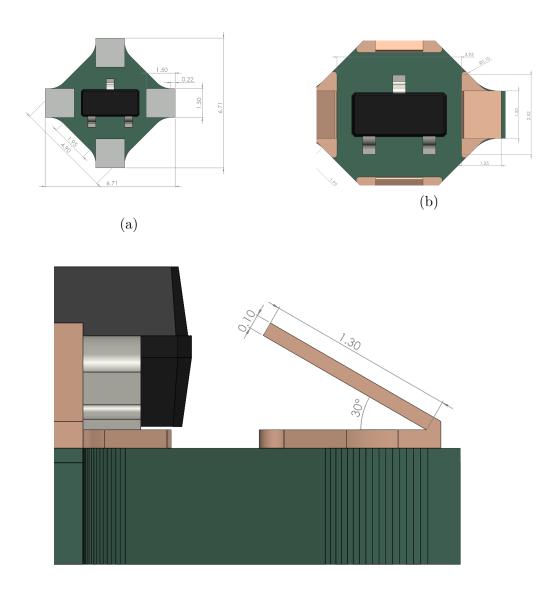

| 5.8 4BIc dimensions: bare 4BIc0 tile dimensions (a), 4BIc tile with contacts (b), side                        |

| view of the contact geometry (c)                                                                              |

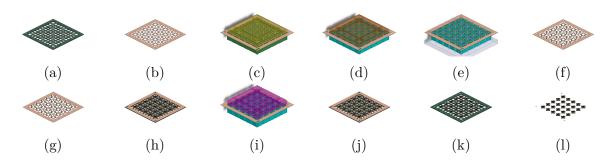

| 5.9 4BIc process steps: (a) PCB 5x5 v-cut panel of sot323 tiles, (b) Fiber laser-cut                          |

| leadframe, (c) Eject trash for solder rivets later, (d) Form 1: 90 degree bend, (e) Eject                     |

| leadframe, (f) Formed leadframe 1, (g) Flip over, (h) Register against PCB for reflow                         |

| step, (i) Form 2: 60 degree bend, create compliant contacts, (j) Formed leadframe 2, (k)                      |

| Laser Singulation: remove leadframe tie-bars, (l) Tool Singulation: shear PCB v-cuts 89                       |

| 5.10 4BIc assembled into a circuit                                                                            |

| 5.11 Laser-marking soldermask for differentiating sides                                                       |

| $5.12~0.127\mathrm{mm}$ C510 lead<br>frame fabrication with the F1 Ultra $\ldots \ldots \ldots 91$            |

| 5.13 Tool assembly process: the print is post-cured in the Form Cure to maximum                               |

| strength properties (a), parts, particularly the mating clamp, are checked for clear                          |

| channels (b), tools are installed into their receptacles (c), the top half is then loaded                     |

| onto the linear guides (d), the tool is loaded into the arbor press (e), and then the press                   |

| is actuated and the lead<br>frame has been modified, whether ${\rm ejected}/{\rm formed}/{\rm singulated}~92$ |

| 5.14 The Form tooling process                                                                                 |

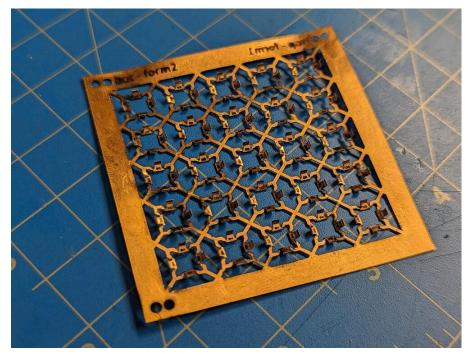

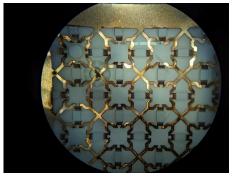

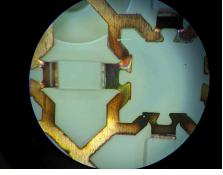

| 5.16 Formed lead<br>frame, with revised geometry solving earlier problems $\ldots \ldots 94$                  |

| 5.17 The second form operation, which uses slanted tooling features to form the final                         |

| leaf spring contacts                                                                                          |

| 5.18 Tile singulation tool                                                                                    |

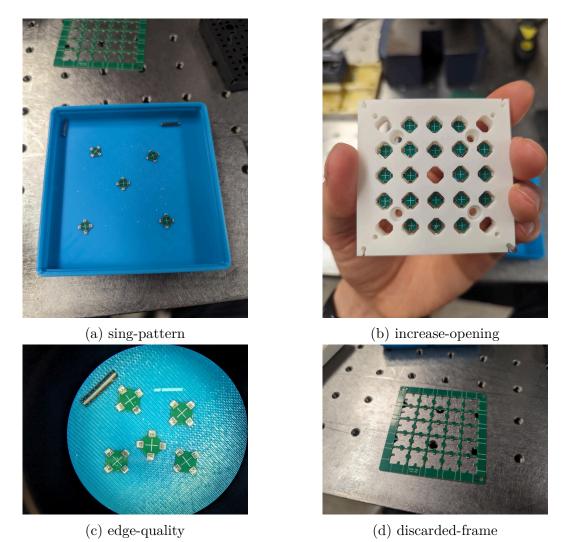

| 5.19 Singulation troubleshooting: The first singulation left a pattern that correlates                        |

| with the first wave of punches (a), the rest were stuck in the clamp (b). Increasing the                      |

| opening of each of the windows resolved the issue. After $\sim 20$ singulations, edge quality                 |

| seems to be fairly consistent (e)                                                                             |

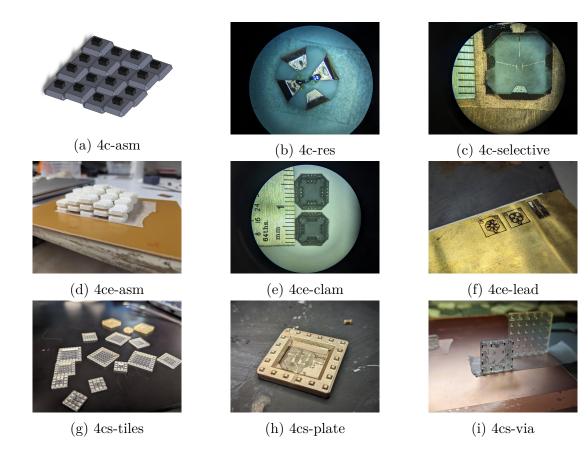

| 6.1 4Cx family of geometries                                                                                  |

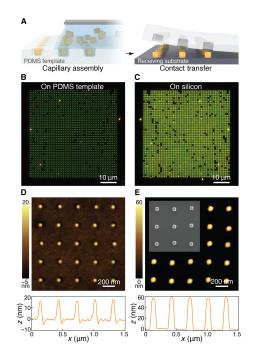

| $6.2 \sim 55$ nm gold nano cubes undergoing contact printing for precise, scalable, and                       |

| pristine particle patterning, $[64]$ 102                                                                      |

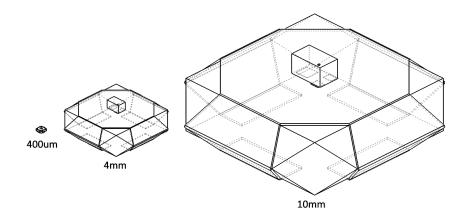

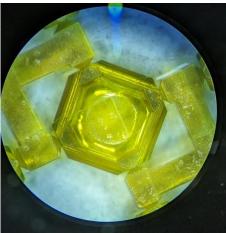

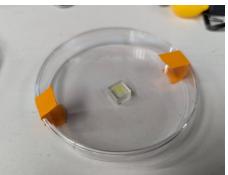

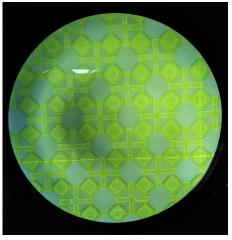

| 6.3 4Cx VMD prototypes (with pockets for integrating components) printed on the                               |

| UpNano One 2-photon printer 103                                                                               |

| 6.4 Super-DICE 2.0: AQFP buffer device designed by Camron Blackburn et al [69] (a),                           |

| Concept layout for Super-DICE 2.0, Camron Blackburn's sketch (b)105                                           |

# List of Tables

| 2.1 Geometry feature comparison                                        | 30 |

|------------------------------------------------------------------------|----|

| 3.1 Pick and Place Machine CPH Comparison spanning multiple categories | 58 |

| 3.2 Selected PnP machines for projections                              | 59 |

| 3.3 Parallelization pnp projections                                    | 59 |

| 4.1 Parasitic resistance measurements for each sample                  | 68 |

| 4.2 the resulting Normal Force Window for all 4 samples                | 69 |

# **1** Introduction

# 1.1 Motivation

Moore's law originated with Gordon Moore, who in 1965, observed that the number of transistors on an integrated circuit were doubling every two years. Later revised to every 1.5 years, Moore projected that transistors were on track to continue this trend for the next 10 years.

The practical implementation of Moore's law was initially enabled by Dennard scaling, a principle formulated by Robert Dennard in 1974. Dennard scaling suggested that as transistors shrink, power density remains constant, allowing smaller transistors to operate at lower voltage, higher speeds, and with better power efficiency. This complementary principle meant that not only could more transistors fit on a chip (following Moore's law), but they could also operate more efficiently, creating a self-sustaining cycle of performance improvement.

In fact, for the past 50+ years, Moore's law has largely dominated the exponential performance increase seen by the computing industry, but due to the breakdown of Dennard scaling around 2006 [1] and physical limits, many have proclaimed Moore's law dead [2]; [3]; [4]. Without Dennard scaling's benefits, increased transistor density no longer automatically translates to proportional performance and efficiency gains. Transistors are still being improved [5], but no longer at the pace of Moore's law, and with a higher price tag [6].

The end of Moore's law has brought about demand for alternative solutions to continue increasing performance in lithography. This has placed a lot of focus on new approaches such as the Gate All Around FET (GAAFET) [7], back-side power delivery to alleviate on-device wiring density [8], and High-NA Extreme Ultra-Violet (EUV) lithography [9]; [10]; [11].

In particular, chiplets and heterogeneous integration (HI) [12]; [13] are a packaging innovation that enables designers to bring critical circuits closer together and fab designs on process nodes suitable for each chiplet, rather than compromising performance by using one node for the entire die, which can be challenging and expensive; power, compute, and MEMs all have different requirements, and different nodes are better for optimized for different applications.

While HI is now considered a mainstream advanced packaging technique that has allowed the industry to continue scaling performance, many of the viable implementations are still limited in the number of chiplets they can stack and interconnect; true 3d packaging without restriction is still out of reach, economically and technically. And while the semiconductor industry has access to HI, the rest of the electronics packaging stack has not been similarly improved, which reduces the effectiveness and accessibility of gains made in the semiconductor industry.

In this thesis, I focus on ground work developing the Volume Mount Device (VMD), a term initially coined by Ahmad Bahai and Neil Gershenfeld. This new packaging standard aims to eventually replace SMD and enable true 3d heterogeneous integration, refactoring the entire electronics stack instead of a small portion of it.

### 1.2 Electronics Packaging

Electronic packaging refers to the design and production of enclosures for electronic devices ranging from individual semiconductor devices up to complete systems. Packaging must address critical constraints including protection from mechanical damage, cooling, electromagnetic interference (EMI), and electrostatic discharge.

The conventional electronics packaging (EP) paradigm describes how electronics are physically packaged across multiple levels, from semiconductor devices to complete systems:

Figure 1.1: Hierarchy of electronics packaging levels. Level 0 represents the bare die (transistors). Level 1 is the integrated circuit (IC) package. Level 2 consists of the substrate (e.g., PCB). Level 3 refers to the full system.

This EP structure describes the physical hierarchy of electronic systems, while the OSI model describes the digital communication hierarchy. Interconnects between these levels form their own hierarchy, often denoted as "half-levels" (0.5, 1.5, 2.5), representing the critical interfaces between major electronics packaging levels.

While this established EP hierarchy has enabled tremendous growth in computing capability, we're now facing challenges with greater compute demands, power constraints, thermal limitations, and efficiency requirements. The semiconductor industry has responded with advanced packaging approaches, but these innovations have primarily focused on level 0 and 1, with limited transformation at higher levels.

#### 1.2.1 Printed Circuit Boards

Printed circuit boards have evolved dramatically since Paul Eisler created the first true PCB in 1936 [14]. From simple single-layer boards to today's complex high-density interconnect (HDI) PCBs with embedded components and 3D architectures, this technology has consistently improved to meet miniaturization and performance demands.

Despite these advances, multilayer PCBs remain accessible only at premium prices, and global supply chain disruptions (such as the COVID-19 pandemic [15] and trade tariffs [16]) have revealed significant vulnerabilities in this approach. And while a quick-turn PCB can be had in as little as a week, the centralized nature of manufacturing creates bottlenecks that can delay development by weeks or months. Decentralized means of PCB fabrication, such as cnc milled and laser ablated FR1 boards, are regularly used by fablabs, research institutions, and companies that need to quickly prototype, but these fabrication approaches usually don't meet feature parity with ordered PCBs.

#### 1.2.2 Integrated Circuit Packaging

IC packaging has similarly evolved from simple through-hole DIPs in the 1960s to today's complex system-in-package designs. Surface-mount technology (SMT) became the dominant approach in the 1980s and 1990s, fundamentally changing electronics manufacturing while creating a standardized approach for component integration. And while SMT packages have progressively gotten smaller (BGAs and WLCSPs, 008004 and 006003 [17]; [18]), they've fundamentally remained the same as flat devices mounted to a flat substrate.

The biggest change to SMT has been occuring inside the package. Rather than relying solely on transistor scaling, HI focuses on integrating separately manufactured components into higher-level assemblies that provide enhanced functionality and improved operating characteristics. These assemblies are then typically still packaged as SMDs.

### 1.2.3 Heterogeneous Integration

Figure 1.2: Different Heterogeneous Integration approaches

Heterogeneous integration represents the semiconductor industry's embrace of modularity principles. By moving away from monolithic designs toward chiplet-based architectures, manufacturers can mix specialized components fabricated in different process nodes to optimize performance, reduce costs, and improve yields.

The evolution from 2.5D integration (lateral arrangement of chiplets on an interposer) [19]; [20]; [21] to 3D (vertical stacking) [22]; [23]; [24] and now 3.5D [25]; [26] approaches (combining both strategies) demonstrates the industry's commitment to modularity as a path forward. Companies including AMD, Intel, TSMC, and Broadcom have pioneered commercial implementations of these technologies, with initiatives like Universal Chiplet Interconnect Express (UCIe) and Bunch of Wires (BoW) [27]; [28] attempting to standardize interfaces between components.

However, despite the performance gains made, heterogeneous integration approaches remain largely inaccessible to all but the most well-funded organizations due to several significant constraints.

HI technologies require advanced manufacturing capabilities exclusive to major semiconductor companies and foundries, while the specialized equipment, processes, and expertise involved impose prohibitive costs for smaller organizations. The integration of chiplets demands sophisticated thermal, mechanical, and electrical co-design capabilities that exceed what traditional EDA tools can provide [29]; [30]; [31], and the highly specialized nature of HI manufacturing introduces new supply chain vulnerabilities rather than mitigating existing ones. While proving to be a way forward, this concentration of capability limits innovation to a select few industry giants.

# **1.3 Supply Chain Challenges and Climate Implications**

Electronics supply chain disruptions during COVID-19 created year-long lead times for integrated circuits critical to industries such as automotive and industrial manufacturing [15]. These shortages extended beyond ICs to materials like copper foil [32], impacting PCB production. Global trade tensions and tariffs have further exacerbated these vulnerabilities [16].

Despite government initiatives like the CHIPS Act [33]; [34]; [35] in the United States, robust solutions to supply chain resilience remain largely unimplemented. The centralized nature of electronics manufacturing creates fundamental vulnerabilities that legislation alone cannot address.

Furthermore, as computational demands grow (in particular with the surge in AI, large language models, and training infrastructure), the environmental impact of electronics manufacturing becomes increasingly significant [36]; [37]; [38]. Without more efficient approaches to electronics packaging and assembly, the climate impact of computing will likely worsen dramatically in coming years.

# 1.4 Accessible Modularity

Previous research in discretely assembled electronics has demonstrated potential for addressing both performance and supply chain challenges. Modular approaches have shown promise for both high-performance computing systems and lower-level electronics packaging, though physical implementations have typically been limited to tens of components rather than the hundreds or thousands needed for practical applications.

The challenge lies not only in technical feasibility but in creating solutions that remain accessible after implementation. Desktop-scale discrete electronics assembly offers a complementary approach to traditional manufacturing; not replacing it, but providing flexibility through localized assembly using standardized components sourced through diversified supply chains.

# 1.5 Related Work

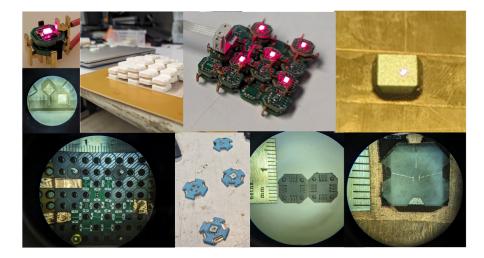

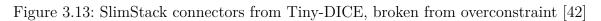

Figure 1.3: Digital electronic materials history, Neil Gershenfeld

### 1.5.1 Project Tinkertoy

The concept of modular electronic systems is not entirely new. In the 1950s, when PCBs already existed but most electronics were still manually assembled via labor-intensive methods like wire-wrapping [39]; [40], the U.S. National Bureau of Standards developed Project Tinkertoy [41], a pioneering modular electronics approach that used standardized ceramic wafers as building blocks for electronic circuits. These modules were designed to snap together to form functioning circuits, and although it was eventually superseded by PCBs and transistors, it played a large role in establishing the automation that drives those processes today.

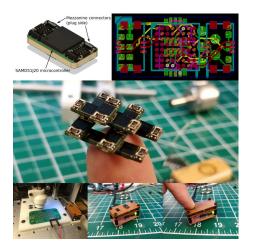

### 1.5.2 Electronic Digital Materials

In the past two decades or so, more recent work has been done on electronic digital materials, a contemporary rebirth of the ideas that Project Tinkertoy put forth. These implementations have been explored from a variety of angles and abstraction levels by Fredin [42], Langford [43], Ward [44], MacCurdy [45], Hiller [46], and others.

These range from basic conductive and insulating elements, as demonstrated in Ward's discretely assembled circuits and Langford's GIK passive components, to component-level systems like BitBlox, to highly integrated programmable processor elements like DICE (Discrete Integrated Circuit Electronics).

These projects have demonstrated the fundamental feasibility of discretely assembled electronics but have generally been limited in assembly scale, automation capabilities, and practical applications. The VMD approach in subsequent chapters builds upon these foundations while addressing their limitations to create a truly scalable volumetric electronics paradigm.

#### **Basic Bulk Materials**

(a) Ward's discretely assembled circuits

(b) Langford's GIK discretely assembled passives

Ward [44], Langford [47], Hiller, and others have demonstrated basic electronic digital material systems of different geometries at various levels of automation.

In Jonathon Ward's geometry [44], he demonstrates conductive and insulating assemblies up to 100 parts, manually assembled.

Additionally, in the process of building an LC resonator, Will Langford assembled an inductor from 520 parts via the time-honored fabrication process of GSWT (graduate students with tweezers, a manual process) [48].

#### **Component Materials**

MacCurdy et al. Demonstrated the BitBlox platform with two significant implementations. The first was a two-channel infrared remote control constructed from 17 blocks representing 7 distinct functional types. This assembly was completed using an automated process, though no specific assembly time was documented [45]. In a more complex application, they created a five-channel infrared remote control utilizing 130 blocks

(b) Langford's discretely assembled robot

(a) MacCurdy's BitBlox remote

Figure 1.5: Component Materials

across 7 functional types. This larger system was assembled manually and required approximately two hours for both design and assembly tasks [45]. These examples illustrate both the scalability of the BitBlox approach and the potential time efficiency advantages of automated assembly processes compared to manual construction for complex electronic systems. However, the paper also qualitatively suggested that the automated assembly process was only sometimes reliable.

In his PhD thesis, Will also developed a robot assembler for automated assembly, which demonstrates constructing a walking motor from 20 nodes, 6 rigid struts, 4 flexural struts, and 2 actuators; in total, a 32-part walking motor in 8 minutes (4 parts/min, or 240 components per hour (CPH)) [47]. This system could handle 3 different element classes (nodes, struts, and actuators) via toolchanging, and incorporated many quality of life features, such as being able to change part-feeding magazines while jobs were running. However, the assembly rate is slow to build large complex assemblies within a reasonable amount of time; an entry-level desktop pick-and-place (PnP) is 1580 CPH, while this process is 240 CPH.

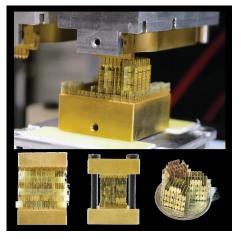

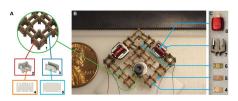

#### Discrete Integrated Circuit Electronics (DICE)

The term Discrete Integrated Circuit Electronics (DICE) was initially coined by Will Langford in his PhD thesis [47], and referred to an integrated electronic digital material design that relied on laminate layers to pack multiple conductive layers into an element.

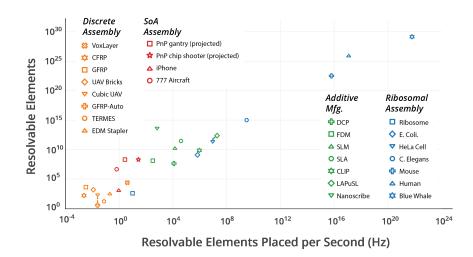

In Tiny-DICE, Zach Fredin designed and fabricated microcontroller assemblies using the smallest COTS components at the time; subcompact mezzanine connectors were used as interconnects for the elements, which were connected in a tetrahedral geometry [42].

His later iteration of Meso-DICE increased the size of the elements to explore more reliable interconnect mechanisms fabricated in-house, and prioritized reliability over feature size.

These geometries were built in 10s of elements, in Tiny-DICE's case, it was a single type, and in Meso-DICE, it was 2 types.

In general, component and integrated level geometries share similar packaging challenges; to route multiple nets and build-in mechanical properties for alignment and retention, feature overhead must be added for reliable operation.

Figure 1.6: Integrated Materials

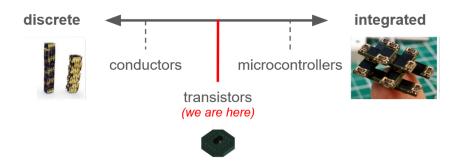

#### Abstraction Levels

Figure 1.7: Component level, in-between basic and integrated

The component abstraction level is the most flexible between basic and integrated, as it can be used for a variety of applications, including computational or power, and provide flexibility in how those applications are implemented. For example, computational architectures could be NMOS, CMOS, diode, etc. Additionally, the component abstraction level can expand to interoperate with basic and integrated abstraction levels easily through a compromise of design requirements; more basic elements can be incorporated by subdividing the component grid and reducing features, and more integrated elements with higher fan-out need only add ports by scaling up in the grid.

Comparatively, operating at the basic abstraction level requires a large amount of assembly to achieve a useful level of complexity; on the opposite end, operating at the processor level greatly reduces design flexibility to only include specific types of computational applications using the same computational architecture, and uses parts with higher overhead that makes it difficult to retool for different use cases.

# 1.6 Thesis Contributions and Overview

This thesis contributes a volumetrically scalable set of electronic building blocks that can be used to build architecturally agnostic computational logic at the component abstraction level, along with an assembly system for constructing sophisticated electronic circuits. Because the component abstraction level is inherently flexible, this system can be repurposed across multiple abstraction levels, from individual logic gates to integrated structures like operational amplifiers and processor cores.

In Chapter 2, I present a systematic exploration of VMD geometries, analyzing the critical design decisions that govern their effectiveness. I examine manufacturability constraints, electrical and mechanical performance requirements, and feature considerations that influenced the development process. This chapter introduces several candidate geometries, from the initial 4H family to the more refined 4B and 4BI implementations, documenting how each iteration addressed limitations in previous designs. I detail how different tile and connector designs affect mechanical stability, electrical performance, and automated assembly capability, establishing the foundation for a viable VMD ecosystem.

Chapter 3 details the circuit assembly system I developed to construct VMD-based circuits at scale. This chapter examines the motion system architecture, specialized feeders for component storage, substrate design for precise positioning, and end effector configurations optimized for reliable manipulation. I present assembly benchmarks that demonstrate the system's progression from handling tens of components to reliably placing hundreds of elements with minimal human intervention. This chapter also analyzes potential fault states and error correction strategies critical for scaling to larger assemblies, representing a significant advancement beyond previous work in modular electronics.

Chapter 4 evaluates the performance characteristics of assembled VMD circuits, focusing on two critical aspects: joint reliability and electrical performance. I present analysis of normal force windows and resistance measurements for different contact implementations. The chapter also showcases some example applications through ring oscillator and logic gate implementations. Performance characterization extends to first-principles projections for scaled-down micro-regime implementations, establishing the performance envelope for future VMD development.

Chapter 5 examines the current and upcoming VMD fabrication processes, with particular focus on the development of the 4BIc geometry. This chapter details my process for rapidly prototyping electrical "Connectors in a Day" (eCiD) using commercially available digital fabrication tools, and documenting the challenges and solutions encountered when developing self-aligning connector interfaces that enhance reliability while maintaining accessibility.

Finally, Chapter 6 concludes with a synthesis of the research findings and outlines promising directions for future work, including potential applications in heterogeneous computing systems, superconducting electronics, and scaled-down implementations approaching the semiconductor integration level. This chapter positions VMDs within the broader context of electronics manufacturing evolution and discusses their potential impact on supply chain resilience and sustainable electronics development. Collectively, these chapters document the development pathway from conceptual design to practical implementation, and aim to establish VMDs as a viable path towards truly volumetric electronics that bridges the gap between conventional packaging technologies and advanced heterogeneous integration techniques.

# 2 Volume Mount Devices (VMDs)

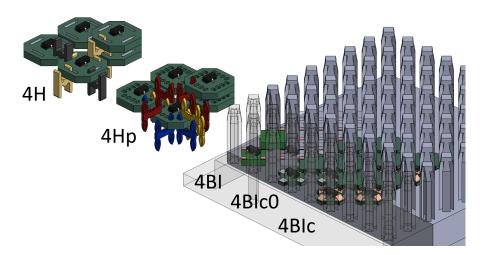

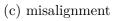

In the current generation of DICE, there have been several geometries, split into families, explored in the process of discovering a geometry that satisfies fabrication, routing, and reliability requirements.

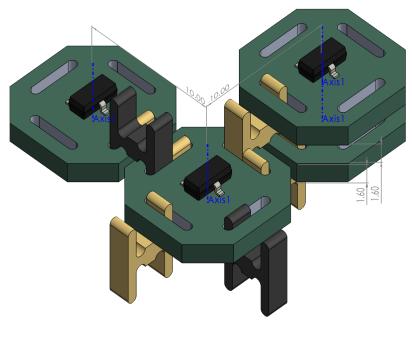

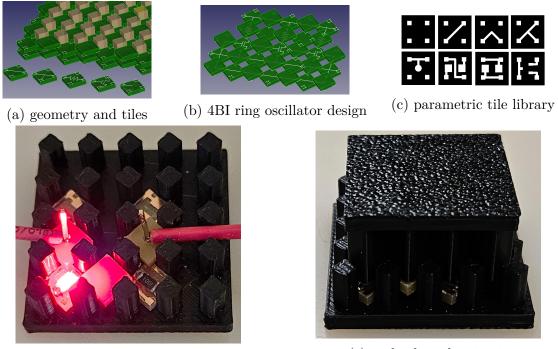

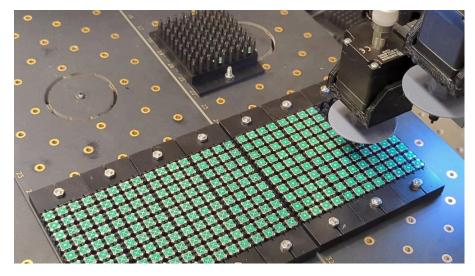

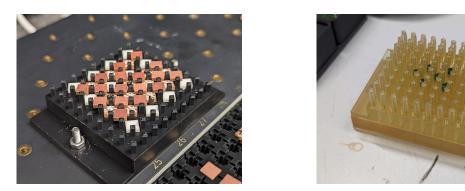

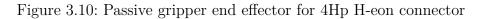

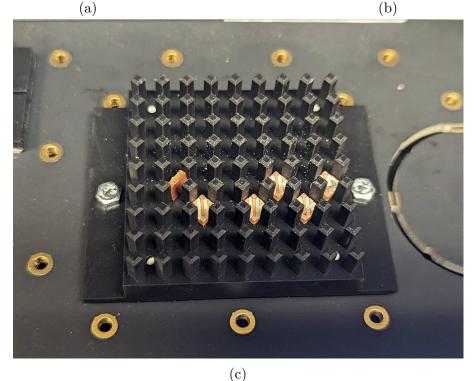

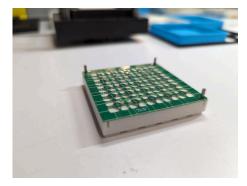

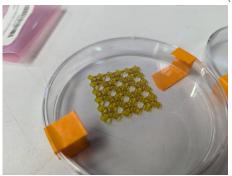

The current active geometry is 4BI, which is stacked in an alternating fashion. This geometry has been used to assemble an 8-layer, 256 tile mechanical benchmark assembly with only 2 faults that required manual intervention, significantly more elements than previous work at this abstraction level.

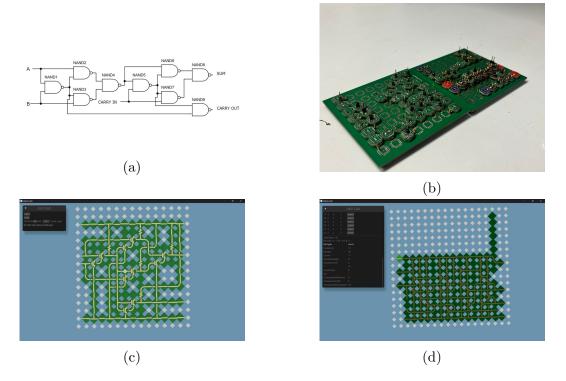

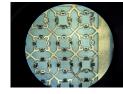

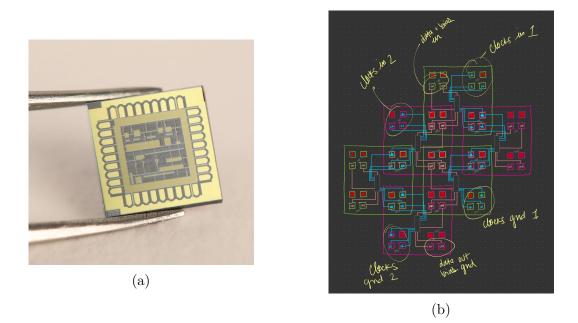

Figure 2.1: 4BIc0 circuit assemblies: 4BIc0 8-layer mechanical benchmark (254/256 tiles) automatically assembled in ~14min (a); 4BIc0 2-layer stackable full-adder circuit (146 tiles) manually assembled in ~55min (b)

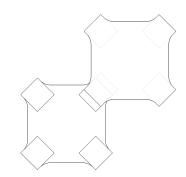

On the way to 4BI, a variety of geometry topologies and configurations were explored in the mm to cm scale (Figure 2.2).

# 2.1 Geometry Overview

The naming scheme is loosely based on (number of edges)(interconnect)(additional descriptors).

- number of edges: typically 4, though there have been experiments with 3-edge geometries

- interconnect: usually the shape of the interconnect itself; 4H refers to the H-shaped connector, 4B refers to two surface mount contacts pressed against each other, and 4BI represents surface mount contacts and alignment pillars <sup>1</sup>

<sup>&</sup>lt;sup>1</sup>credit to Neil Gershenfeld for creating this naming scheme

Figure 2.2: A variety of geometry iterations

Figure 2.3: Fabricated geometry families

• additional descriptors: shorthand for a feature (i for integrated, p for power, k for kinematic, c for connector, 0 for just the PCB)

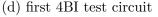

In chronological order, the naming definitions of geometries that made it to fabrication (Figure 2.3):

- 4H: 4-sided, H-shaped interconnects

- 4Hp: 4-sided, H-shaped eye-of-the-needle (H-eon) interconnects

- 4B: 4-sided, B-shaped pad-to-pad interfaces

- 4BI: 4-sided, B-shaped pad-to-pad interfaces, with I-shaped alignment pillars

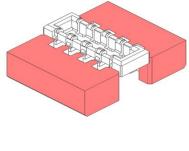

- 4BIc: 4-sided, B-shaped pad-to-pad interfaces, with I-shaped alignment pillars, using compliant connector interfaces

- 4BIc0: a lite-version of 4BIc, using just the PCB. Fabricated and used in the same manner as 4BI.

| Geometry Name     | 4H        | 4Hp       | 4B       | 4BI      | 4BIc0    | 4BIc     |

|-------------------|-----------|-----------|----------|----------|----------|----------|

| Connection Type   | Insertion | Insertion | Pad      | Pad      | Pad      | Pad      |

| Preload Method    | Local     | Local     | Global   | Global   | Global   | Global   |

| Element Types     | 2         | 2         | 1        | 1        | 1        | 1        |

| Dedicated Power   | No        | Yes       | No       | No       | No       | No       |

| Mech. Stability   | Low       | High      | Low      | Medium   | High     | High     |

| Asm. Complexity   | Medium    | High      | Low      | Low      | Low      | Low      |

| Alignment         | Connector | Connector | Template | Template | Template | Template |

| Assembly Force    | High      | Medium    | Low      | Low      | Low      | Low      |

| Joint Reliability | Poor      | Good      | Poor     | Fair     | Fair     | Good     |

| Scalability       | Poor      | Fair      | Poor     | Good     | Good     | Good     |

Table 2.1: Geometry feature comparison

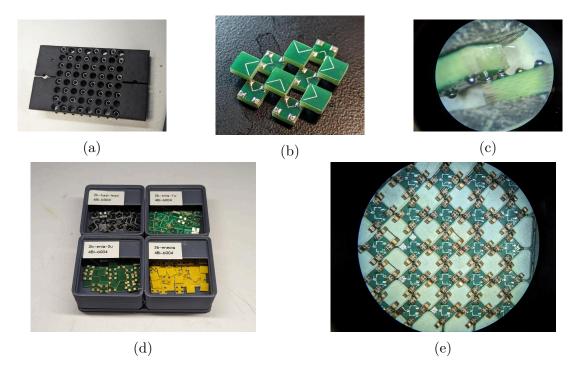

The evolution from 4H to 4BI represented a significant shift in VMD design philosophy (Table 2.1). The 4H family utilized separate tiles and interconnects with through-hole connections requiring local preload, while the 4B family eliminated separate interconnects in favor of surface mount connections with global preload.

The big problem with the initial 4H geometry was a lack of contact compliance and interconnects with non-uniform strength properties. The 4Hp approach offered better joint reliability and uniform strength properties through a single compliant connection design but suffered from high insertion forces and complex assembly requirements.

The transition to 4B significantly simplified assembly by eliminating the separate interconnect elements altogether, but introduced alignment challenges. 4BI addressed these alignment issues through a comprehensive templating system, though at the cost of joint reliability compared to 4Hp.

This evolution demonstrated a trade-off between assembly simplicity and electrical reliability, with each geometry optimized for different aspects of the VMD concept. While 4Hp excelled at creating reliable electrical connections, 4BI proved superior for automated assembly at scale, representing the current active geometry in the VMD ecosystem.

### 2.2 4Hx Family

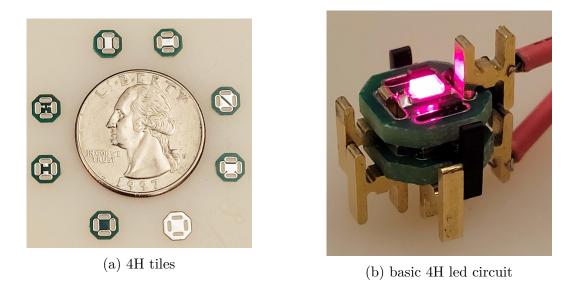

#### 2.2.1 4H

4H represents the initial foundation for the current run of DICE geometries, sometimes referred to as "O's and H's" (Figure 2.4). Its approach distinctly separates tiles and interconnects as fundamental elements, with tiles designed in square configurations and interconnects adopting H-shaped structures. The system employs two distinct tile categories: functional tiles containing a single component, and routing tiles facilitating net movement along a Cartesian grid.

While the 4H design benefits from conceptual simplicity, it presents several significant limitations. The provision for only a single net per edge makes ubiquitous power delivery particularly challenging; additionally, the system's requirement for two interconnect types, conductive and insulative, resulted in inconsistent mechanical rigidity, which distorted the lattice structure and compromised assembly consistency.

The H-shaped interconnects lacked geometric compliance, causing all ports to rely solely on press-fit mechanisms and the compliance of bulk materials, which introduced unreliable forces, especially where geometric tolerances were poorly controlled; these tolerance issues proved especially difficult to manage given the large quantity of components needed and the outsourcing of designs to board houses, further complicated by designing at the boundary between reasonable size and achievable tolerance levels. An additional challenge was the single slot intended for two H's; a single H could leave the system underconstrained and theoretically introduce assembly error.

#### 2.2.2 4Hp

4Hp, previously named o\_power, represents an iteration over the 4H design that introduced additional ports for dedicated power delivery and mechanical stability, along with compliant H interconnects (Figure 2.6). This evolution addressed several key limitations of the original 4H approach while maintaining its fundamental architecture.

The 4Hp design achieved notably improved mechanical stability, though the seating issue remained difficult to tune properly. This enhanced stability enabled consolidation to a single H-interconnect type (conductive only), resulting in more reliable mechanical behavior throughout the system. The introduction of dedicated power ports enabled ubiquitous power delivery across the grid, addressing one of 4H's primary limitations.

By pushing our H-connector element towards more compliant designs, we improved the reliability of each connection and increased the possible lifetime mate cycles. Eyeof-the-needle (EON) compliant designs were heavily used in the connector industry for automotive and other high performance applications. Compared to other compliant designs, EON features were easily scaled down [49]; reducing connector size with respect to tile size enabled us to move away from slots towards holes, increasing connection density on each tile. This allowed us to add dedicated power delivery connections both laterally and vertically, which also worked to improve the overall stiffness and mechanical consistency of the structure during assembly.

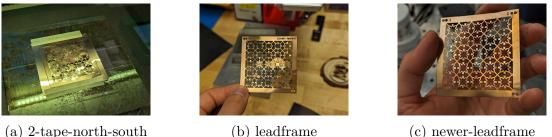

These connectors were fabricated from 0.6mm C510 Phosphor Bronze sheet stock, cut

(b)

(c)

Figure 2.4: 4H dimensions: the tile (a), the H connector (b), and the lattice (c)

Figure 2.5: 4H overview

using the Fablight, a 3kW fiber laser (Figure 2.7). Initially, the H-eon connector geometry was compromised and plastically deformed after repeated cycles because the oval was cutoff; as shown in Figure 2.8a, I incorporated several quality-of-life design improvements such that the new geometry had a whole oval that was also above the joining strut, so the pin behaved compliantly. Additionally, the new version had an indent to set the tiebar lower into the body; the leftover stub would protrude from the design and prevent the connector from seating properly, and this feature made the connector behave in a flush manner.

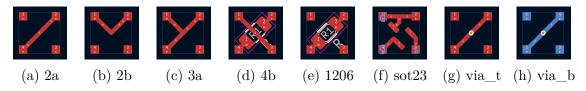

To build basic logic gates and other circuits, we developed a 6-tile library that consists of both functional tiles for components and routing tiles. As shown in Figure 2.9, routing tiles enable connecting nets to power or to selectively direct signals in different directions. This tile system maintains dedicated power ports for each side, located in such a way that structural stability is maintained while being able to selectively populate signal pins.

The introduction of dedicated power ports were not without cost. To avoid adding too many pins to each tile which would make it harder to shrink the design for future, higher density revisions of the geometry, a minimal number of power ports were added, which meant symmetry across the diagonal of the tile, but not axially. This meant that introducing any new tile would also necessitate adding a few variations to enable all possible routing orientations. As a result, additional tiles were introduced for easier implementation of NMOS logic, such as pull-up resistor tiles and FETs covering various degrees of freedom.

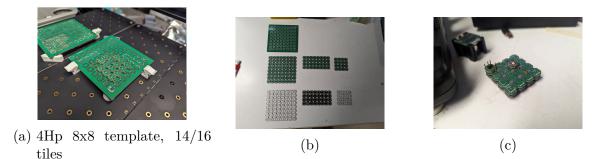

Additionally, I designed macro-tiles, which were larger tiles that were ordered in sizes of 4x4, 4x8, and 8x8, used to create sub-assemblies called "blocks", which enable easier assembly/disassembly, or error correction, for larger structures. The structure is shown in Figure 2.11.

Despite improvements over 4H, 4Hp introduced several new challenges. The dedicated power ports led to significant assembly scale issues, with interconnect pick-and-place op-

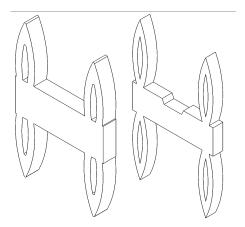

Figure 2.6: 4Hp: the tile (a), the connector (b), and the lattice (c)

Figure 2.7: Top: H-eon, from cad to fab, Bottom: 4Hp tile, from cad to fab

(a) left, v1.0; right, v1.1 connectors (

Figure 2.9: left, basic 6-tile library; right, implemented power, ground, and signal mapping for tiles

Figure 2.10: 4Hp Batch 009 tiles

(a) 4Hp 4x4x4 circuit

(b) 4Hp hierarchy

erations dominating assembly complexity at approximately a 4:1 ratio against tiles. The partially symmetric power ports also led to a combinatorial explosion of additional tiles to maintain design freedom, making designs more complicated and less flexible. Interconnect tolerances proved difficult to control tightly and were challenging to outsource using rapid prototyping fabrication houses. Additionally, interconnect pick-and-place operations proved less reliable than tile placement. The connection mechanism operated contrary to zero insertion force (ZIF) principles, functioning more like "much insertion force" (MIF); this high insertion force would frequently lead to component damage in common misalignment scenarios, as well as loss of stepper motor steps during assembly operations.

# 2.3 4Bx Family

# 2.3.1 4B

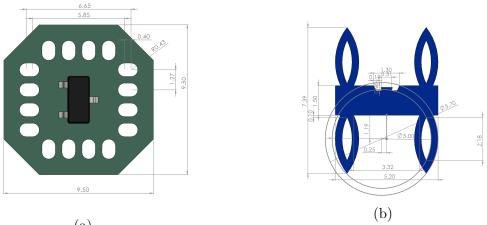

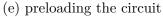

4B represented a significant departure from the 4Hx family, eliminating the separate interconnect primitive in favor of using tiles only (Figure 2.12). This simplification offered the advantage of requiring only one end effector approach for a single primitive type, streamlining the assembly process. However, the 4B geometry introduced its own set of challenges. Since components remained on the tiles, the assembly process required either inverting the tiles or changing the end effector nozzle size to accommodate varying component dimensions. More critically, this geometry inherently lacked the templating and alignment features necessary for automated assembly, making it impossible to scale assembly without accumulating significant error.

(a) 5mm 0603 tile

(d) Ring oscillator circuit

(b) 4B tile feeder

(e) Assembly without alignment

(c) Alignment template

(f) Mis-alignment

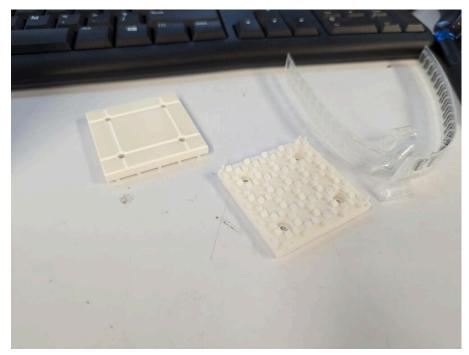

Figure 2.12: 4B design and assembly tests

To optimize the geometry for scaling down to smaller regimes, these new geometries were developed specifically to eliminate interconnect components. While 4B incorporated an initial alignment template, subsequent layers were left under-constrained, inevitably leading to cascading misalignment errors that compromised system integrity and reliability.

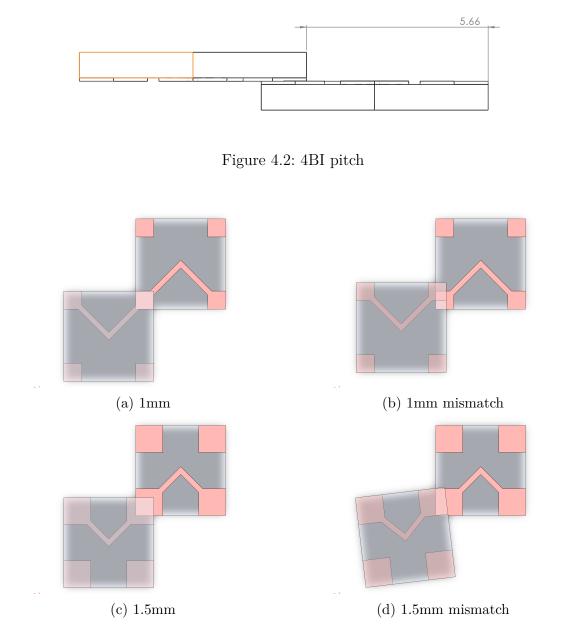

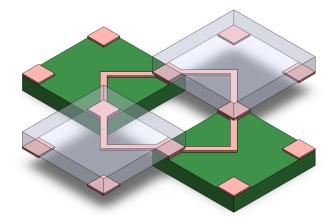

Figure 2.13: 4BI dimensions: 4BI tile (a), 4BI lattice pitch (b), 4BI template top down (c), template corner features (d), and side profile of flexures (e)

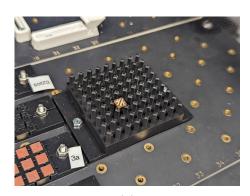

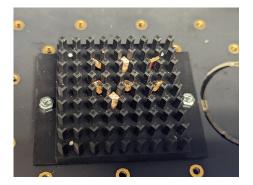

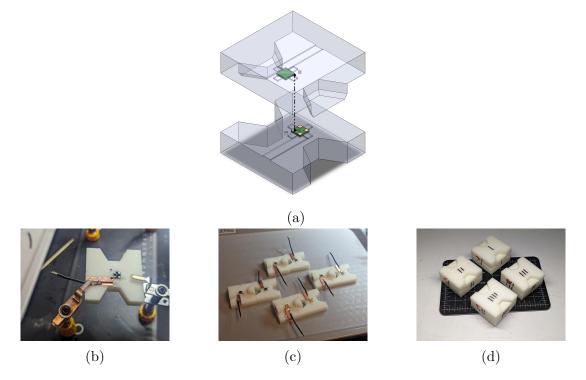

4BI represents the current active geometry in the DICE ecosystem, serving as an iteration built upon the 4B foundation, but introducing a template that works for assemblies larger

than a single layer (Figure 2.13). This approach introduces significant improvements in alignment capability, though initial prototypes featured templates lacking compliant alignment features, creating a suboptimal tradeoff between pick-and-place accuracy and constraint. Subsequent iterations integrate flexures which effectively address this limitation. Compared to 4Hp, 4BI significantly improves assembly yield. Like 4B, 4BI's alternating structure includes gaps that prevent components from interfering with neighboring tiles.

The 4BI approach (Figure 2.14) demonstrates the first version of a geometry that properly utilizes an external structure (the template and the compression cap) for mechanical constraint; this simplifies the pick-and-place process by reducing forces during component placement and relaxing tolerances, as evidenced by later versions of templates with compliant pillars.

Figure 2.14: initial 4BI geometry concept and prototypes (Neil Gershenfeld)

4BI tiles are all 1-layer PCBs, except for special via tiles which are 2-layer. Because dedicated power ports are no longer present in the geometry, tiles avoid the asymmetry problems present in 4Hp, however, the tradeoff is additional tiles required for power delivery within circuits. This leads to a much smaller, manageable set of tiles, which also makes scaling to larger circuit assemblies easier (Figure 2.15, Figure 2.16).

Despite these advances, 4BI introduces several notable constraints. Because the geometry introduces regular pillar features, macro-tiles have less design freedom and face fabrication challenges, since they need to accommodate holes for the pillars. Discrete joint reliability proves reliable for small circuits, but substantially worse than the 4Hp approach as circuits get larger, and the system lacks ubiquitous power distribution ca-

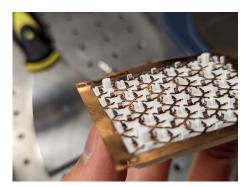

Figure 2.15: 4BI tiles

Figure 2.16: 4BI tiles in gridfinity bins for storage (a), and tiles loaded in a feeder for assembly (b)

pabilities (for now). The 4BI approach relies heavily on global preloading to ensure reliable joints, which significantly restricts structural design freedom; this implementation strongly suggests that gaps can't exist in the lattice structure for reliable global preload to function properly.

In a sense, 4BI is a reshuffling of forces; instead of high insertion force causing troubles during assembly, the same forces must be present post-assembly for the circuit to work.

In the following chapter, I detail the development of an automated assembly system centered around the LumenPnP capable of constructing VMD-based circuits at scale. This system represents a significant advancement beyond the manual or limited automation approaches documented in prior work. By addressing key challenges in motion control, component feeding, substrate design, and manipulation, I demonstrate how VMD elements can be assembled efficiently and reliably. The resulting system not only proves the viability of the VMD concept but establishes a pathway toward scaling to the hundreds or thousands of elements required for practical applications.

# 3 Circuit Assembly System

To automatically assemble these geometries, a motion system and end effector suitable for reliably manipulating these geometries is necessary. The two most viable approaches are mechanically gripping and retaining by friction, and pneumatic pick up.

In this chapter, the assembly system will be described and specific modifications for each geometry detailed. Geometries will then be compared and contrasted on their ease of scalability.

Scalability refers to ease of automated assembly, including fabrication and assembly of the elements (tiles and connectors) themselves, and assembly of circuits using the elements as feedstock. Yield at each stage is important, as well as cycle times.

To implement applications of sufficient complexity, circuits on the order of at least 100s of elements need to be assembled, as partially demonstrated from the related work described in Chapter 1. In our context, 10s of tiles are enough to demonstrate basic functional circuits, such as a NAND gate or ring oscillator, 100s of tiles are enough to demonstrate a full-adder, an important functional block towards a computer.

# 3.1 Assembly

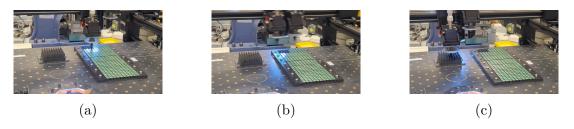

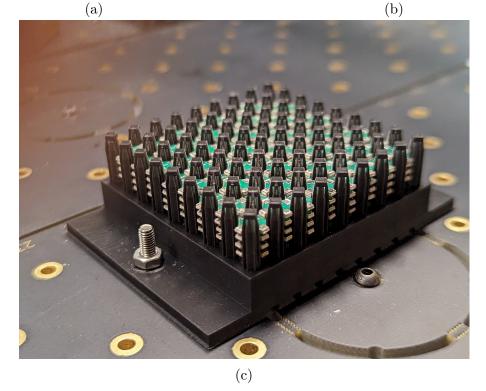

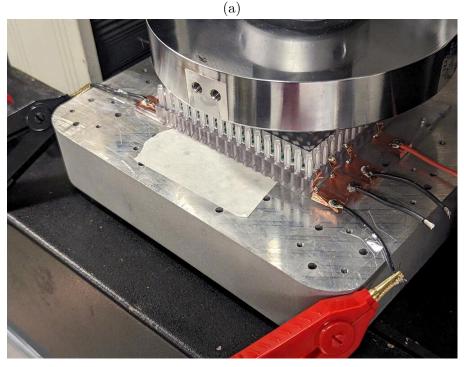

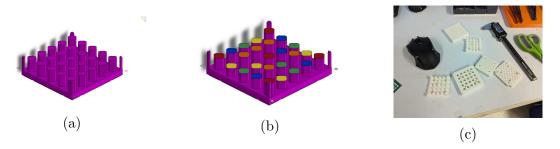

Over the course of assembly testing, multiple placement benchmarks were achieved, starting from 4Hp. The majority of the benchmarks were conducted using the 4BI geometry, since it is designed to scale better. These benchmarks are shown in Figure 3.8.

The flow of operations for assembly of VMD circuits is essentially the same as using a traditional pick-and-place, but adjusting the z of successive components for each additional layer (Figure 3.2).

# 3.1.1 Setup

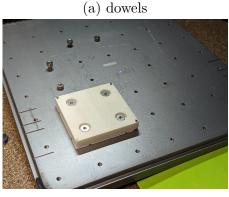

First, the feeders and substrate are installed into the machine. These are currently Form 4 Black V5 resin prints that have been printed flat on the bed; this makes sure that surfaces are as flat as possible from the printer and precludes need for support. They are installed using M3 screws and nuts.

Then, tiles are loaded into feeders, organized by type, with consistent orientation.

Next, the substrate (build platform) is installed. I try to keep the feeders and substrate relatively close to reduce travel time. If the cameras are being used, that's a good place to locate them near, but the stock configuration seems to put more tension on the camera/main platform for the LumenPnP so I prefer to use the auxiliary platforms for my substrate and feeders.

(a) 4Hp 8x8 template, 14/16 tiles

(c) 4BI  $8\mathrm{x}8\mathrm{x}5$  template, 157/160 tiles

(b) 4BI 8x8x2 template, 41/43 tiles

(d) 4BIc0 8-layer template, 254/256 tiles

Figure 3.1: Benchmark tests

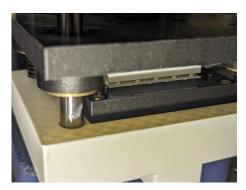

Figure 3.2: The assembler picking and placing from 4BIc0 feeders

With everything installed, I pass a pnp job (.pos, or .board.xml, the native OpenPnP format for jobs) into OpenPnP, run calibration on the feeders and substrate, and press go.

## 3.1.2 Operation

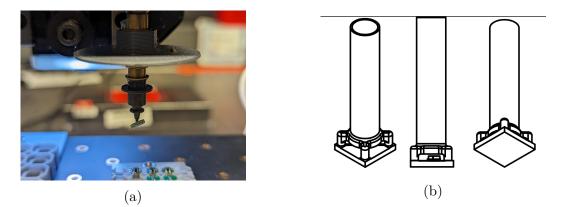

The head moves to the feeders, picks up a part, goes to computer vision, checks part orientation, goes to substrate, places part, and repeats this process until job finish, or as a fault occurs. The basic steps are shown in Figure 3.3.

Figure 3.3: Basic PnP operation (without computer vision): picking (a), moving (b), placing (c)

# 3.2 Motion System

Off-the-shelf open source desktop pick and place machines have matured to the point that it makes sense to use that as a starting point and see how far assembly can be scaled using this motion system. Designing around an existing system allows us to allocate more resources towards geometry development relative to the assembly system.

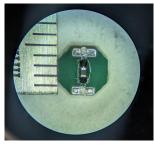

The LumenPnP (Figure 3.4) is a CoreXY motion system with a relatively low z travel, optimized for 2D pick and place operations. In our packaging system, the LumenPnP is used for 2.5D assembly.

# 3.3 Feeders

Feeding is an integral part of the assembly process; as assembly complexity increases, the need to feed higher volumes of primitives increases as well. Resetting jobs manually with tweezers becomes increasingly limiting without automation in the loop.

# 3.3.1 Passive Tray Feeders

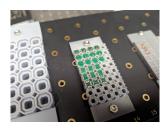

Passive tray feeders were found to be the best fit for initial pick and place operations, initially designed using solidworks, then formalized with feeders.py (cadquery), a parametric script subsequently used to generate arbitrary feeders for both the pnp process and other fab work holding and feeding.

The geometry and its associated infrastructure (feeders for holding the parts, end effector to pick and place the parts, template to receive the parts), were initially designed

Figure 3.4: LumenPnP

in SolidWorks, a parametric point-and-click MCAD tool. In some cases, such as the 4Bx family templates and feeders, designs were then migrated to CadQuery 2, a parametric scripted MCAD tool. CadQuery 2 offers performance and organizational advantages, namely the python support which makes headless automation and scripting with external libraries easy (versus something like the SolidWorks or Fusion360 API). This supports our bottom-up (dice\_cad) and top-down design tools designed by my colleague Erik Strand. Feeders are shown in Figure 3.5.

# 3.3.2 Adding Depth

As assembly transitioned from 10s to 100s, depth was added to feeders to save on xy travel as well as pnp work area. For 4BI, a depth of 3 tiles (of 1.6mm each) was found to be a reasonable capacity; larger than 3x became difficult to load tiles in the correct orientation.

Packaging changes introduce additional challenges for feeding; simple 2d tiles (such as PCBs) have a predictable z-thickness, but packages with compliant flexures have variable z-thickness under load (4BIk) (such as during pick and place) and packages that have been balled (4BIb) (BGA) are subject to additional tolerance stackup based on control of solder sphere tolerances. For exceptionally varied packages, tile planarity also becomes an issue (4BIb?), which needs to be controlled by the feeder geometry itself.

Figure 3.5: Parametric feeder design in CadQuery: 30 element capacity 3x10\_feeder (a), 60 element capacity 3x20\_feeder (b), 60 element capacity 6x10\_feeder (c); evolution of feeder concepts for 4Hp, from trays to magazine dispensers (d)

## 3.3.3 Alternative Feeders

There are many other types of feeders beyond passive tray feeders, such as tape feeders, or vibratory bowl feeders. [50] Traditionally, 1000s of components are likely to be packaged in tape-and-reel. To maintain compatibility between our tiles and industry standard tape-and-reel for feeding, 8mm and 12mm wide tapes would be ideal. Tape and reel introduces additional packaging challenges and tolerance stackup. An alternative approach to active feeding of arbitrary geometries is vibratory feeders. Vibratory feeders come in a couple of flavors, including dish and linear. The main advantage of a vibratory feeder setup is being able to sort loose parts for predictable pick and place. These systems can be combined with computer vision for additional or complementary error correction of part orientation.

## 3.3.4 Resetting Jobs

The current tray feeders work reliably and have room for increased density. However, while they are easy to populate for jobs of 10-100 elements, they quickly become tedious to populate with tweezers, both the conventional and vaccuum types. This is especially true when considering orientation (rotationally and flipped) matters. Populating 280 tiles into 7 feeders (4x10) took ~40min by hand, and it happened that this job was purely a mechanical benchmark with dummy tiles that didn't care about orientation; properly orienting tiles would add additional time.

One possible way to tackle this problem is to observe that feeders and templates are both forms of tile storage. Since a feeder can be used to feed tiles for a template, why can't a template be used to feed a feeder? Feeders are optimized for packing tiles in a nonfunctional state for the purpose of having tiles removed, while templates are optimized for constrained structural lattices in a functional state for retaining tiles.

Storage solutions for these opposite states are easy to design for separately, but difficult to bring together; while removing tiles from a feeder should be low-force, removing tiles from a template should be difficult.

# 3.4 Substrates

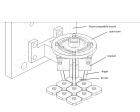

Substrates are large feedstock used as a platform for mechanically constraining and sometimes electrically routing elements assembled into circuits. Related work from Langford [43] and [46] demonstrate uses of substrates for preloading and alignment of elements as well. Two major types of substrates were explored over the course of the geometry design study, the macro-tile from 4Hp, and the template from 4BI.

# 3.4.1 4Hp Macro-tile

The 4Hp macro-tile (Figure 3.6) both provided mechanical support and enabled electrical routing and made breaking out signals easy. Additionally, it was designed with edge tolerances in mind such that tesselating macro-tiles was possible, enabling larger circuits beyond a single macro-tile. However, it made automation difficult; the through-hole

Figure 3.6: 4Hp macro tiles as substrates

connections used to interface with H-eon connectors required higher tolerances, which weren't possible to achieve at scale through the fabrication of H-eon connectors. In addition, 4Hp relied on high insertion forces; this caused the assembler to skip steps during insert, which meant rehoming between each place. In cases of misalignment, this also caused the macro-tile to kinetically discharge chunks of FR4.

Because the macro-tile was a PCB following standard PCB design rules, it wasn't possible to improve lead-in by chamfering the through holes.

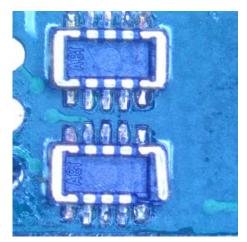

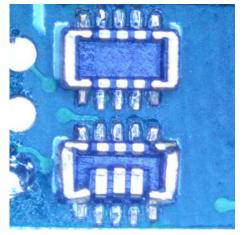

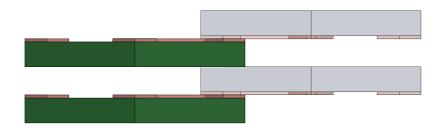

# 3.4.2 4BI Template

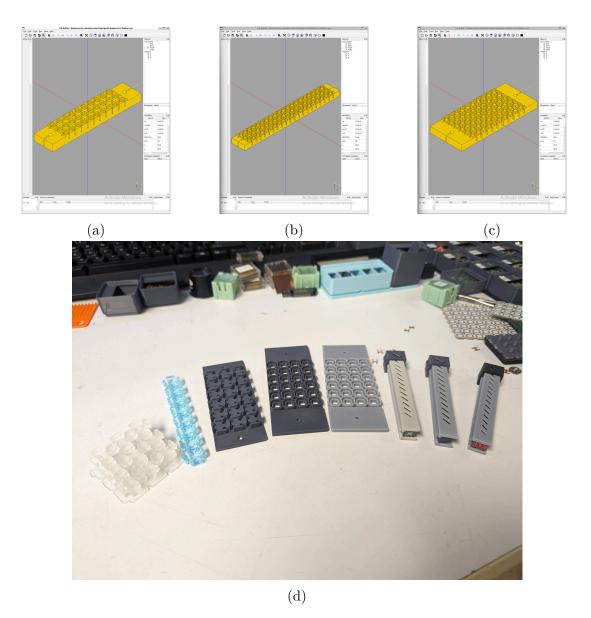

In contrast, the 4BI template is effectively a zero insertion force system. Some common configurations are shown in Figure 3.7.

Figure 3.7: Parametric template design in Cadquery: 9x9x10 template, 320 element capacity (a), 9x9x3 template, 96 element capacity (b), 17x17x10 template, 1280 element capacity (c)

Like their counterpart feeders, 4BI templates were also initially designed using solidworks, then formalized with 4BI.py (cadquery). The current tradeoff between 4BI templates and 4Hp macro-tiles are that while the templates are easier to parametrically generate using 4BI.py, 4Hp macro-tiles are better at tesselation with standardized sizes. Adding this capability to 4BI is on the roadmap. Initial templates used rigid pillars for locating and constraining tiles in xy, subsequent templates implemented compliant pillars that were more forgiving of coarser tolerances, and were important for maintaining pad to pad alignment.

Figure 3.8: Templates in use for various tasks: early rigid template with poor tolerance (a), high-temp reflow variation from soldering tests (b), matured design using Form 4 Black V5 (c)

Over the course of these two jobs we identified problems as well as solutions to increase reliability necessary for automatic placement and avoiding the need for manual intervention. Initial templates featured rigid, non-compliant pillars that ran into tolerance issues; too tight and tiles would bind on the pillars, preventing proper seating and removal, too loose and neighboring pads would misalign and miss, resulting in open circuits. Subsequent templates adopted compliant pillars, which enable tighter tolerances. These new templates guarantee alignment and help retain tiles after placement, which makes assemblies less fragile.

4BI templates also require caps for compression to both preload the entire circuit and increase surface area of contact interface. This concept is similarly applied by [43] in his testing of active components in section 5.2.

#### 3.4.3 Material Choice

During iteration, flexible, elastic resins were considered (such as Form 4 Flex 80A). While these materials offered excellent compliance, they unfortunately exhibited unwanted tackiness that interfered with assembly operations. In addition, the slow springback after deformation was too slow for reliably maintaining xy alignment.

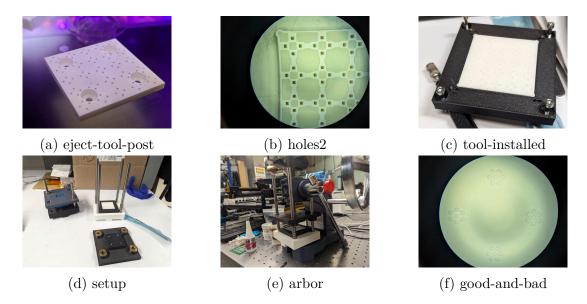

After evaluation, we ultimately stuck with rigid resins with integrated flexures instead of fully flexible templates. This alternative provided more responsive mechanical behavior with less surface adhesion, without compromising the structural rigidity needed for effectively constraining the system during assembly.